Train Crossing Controller: A VHDL Implementation

Academic Project | 2022-2023

In this project, I designed and implemented a digital controller system that emulates the behavior of United Kingdom's train level crossings. The system manages the intricate coordination between train signals, vehicular traffic lights, and pedestrian crossings using VHDL on an FPGA platform. This project demonstrates my expertise in digital systems design, state machine implementation, and hardware description languages.

↓

Technical Challenge

The primary challenge was to create a robust and safe control system that properly sequences multiple sets of signals while maintaining strict timing requirements. The system needed to handle:

Train approach detection and signaling

Vehicle traffic control with amber warnings and flashing red lights

Pedestrian crossing signals with safety timing delays

Real-time coordination between all subsystems

Solution Architecture

I approached this challenge by implementing a finite state machine (FSM) with five distinct states, each representing a different phase of the crossing sequence:

Initial State (State 1): Normal operation with pedestrian green light and train red signal

Warning State (State 2): Amber warning for vehicles while maintaining pedestrian access

Closure State (State 3): All traffic halted with flashing red signals

Train Passing State (State 4): Green signal for train passage

Final Safety State (State 5): Additional safety buffer before returning to normal operation

Key Technical Features

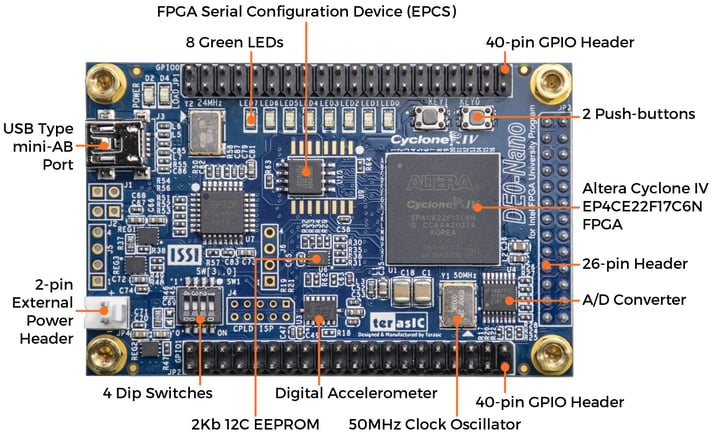

Implemented using VHDL on a DE0-Nano FPGA board

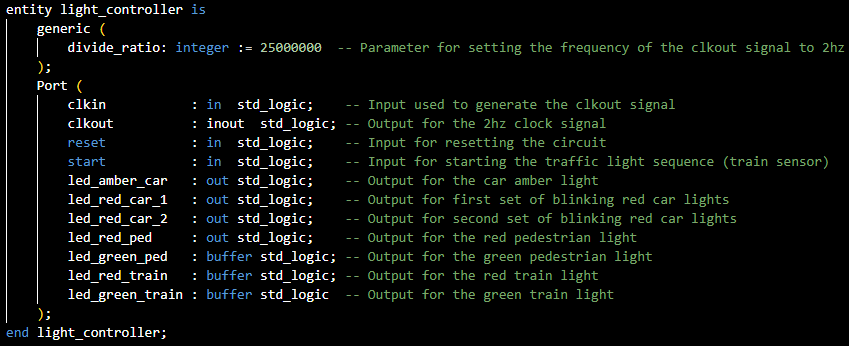

Clock division system generating precise 2Hz timing signals

Modular design with separate clock generation and state machine processes

Fail-safe state transitions with built-in timing constraints

Alternating red signals implementation using modulo operations

Implementation Details

The system was implemented using several key VHDL components:

DE0-Nano FPGA board used to implement the project

The controller uses a carefully timed sequence, with state transitions occurring at specific intervals:

3 seconds for initial warning phase

11 seconds for crossing closure

19 seconds for train passage

27 seconds total cycle time

Testing and Verification

I developed a comprehensive test bench to verify the system's functionality:

Simulated all possible state transitions

Verified timing sequences using ModelSim

Conducted hardware tests on the DE0-Nano board

Created automated test scenarios for edge cases

Skills Demonstrated

Digital Systems Design

VHDL Programming

State Machine Design

Hardware Description Languages

FPGA Implementation

Test Bench Development

Real-time Systems

Safety-Critical Programming

Project Impact

Design complex state machines for real-world applications

Implement safety-critical timing systems

Develop comprehensive test strategies

Create maintainable and well-documented code

Handle multiple concurrent processes

Work with industry-standard hardware platforms

Conclusion

This project demonstrates my proficiency in digital systems design and hardware description languages. It shows my ability to tackle complex control problems while maintaining safety and reliability requirements. The modular design approach and comprehensive testing strategy reflect my commitment to producing high-quality engineering solutions.